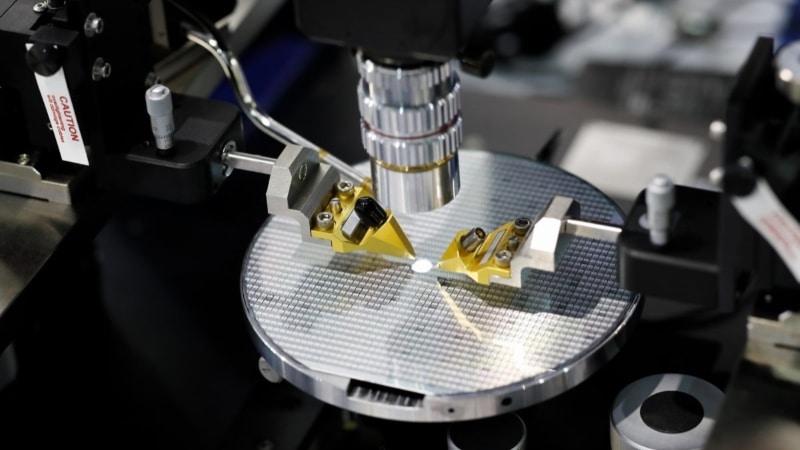

差排這個微小缺陷可能會引發半導體元件的漏電流,進而嚴重影響元件的可靠性。穿透式電子顯微鏡(TEM)是目前唯一能觀察到微小差排的分析工具。TEM可以分析差排的型貌、密度和種類,以及差排在矽基板內的延伸軌跡。

TEM影像的場深和景深

(承前文)圖3是一組簡易的薄凸透鏡成像光路圖(Ray Diagram),左側標示O的黃色箭頭是物體,右側標示I的藍色箭頭是在成像面的倒立放大實像。固定成像面的位置,前後移動物體在Dfd距離範圍內,在成像面上的影像仍在清晰範圍,此Dfd稱為場深(Depth of Field)。

固定物體的位置,前後移動成像面Dfs距離範圍內,在成像面上的影像仍在清晰範圍,此Dfs稱為景深(Depth of Focus)。α角是物體中心點連接透鏡邊緣和光軸的夾角。場深和景深是透鏡的解析度與α角的函數。

一般而言,操作電壓為200KeV的TEM,其場深和景深分別約為400 nm和1000 m。如此大的場深,意指TEM試片內的結構,從表面到底面都在清晰聚焦,所以單從一張TEM影像無法判斷二個特徵物在試片內的相對深度,如圖4(a)中的黃線和藍線。

圖4(a)中的影像對應的顯微結構,可能是圖4(b),也可能是圖4(c)。也就是說,單從圖4(a)一張影像無法作正確的判斷。如果將試片做如圖5(a)的逆時針傾轉某角度後,得到的第二張影像,此時黃藍二線的間距變大,如圖5(b)所示,則可以推斷樣品的結構是圖4(b)的結構,而非圖4(c)的結構。

差排在晶體內的延伸軌跡

在材料學上,差排在晶體某個位置產生後,除非形成一封閉迴路(Loop),否則不會終止在晶體內。所以,半導體元件在離子布植後,因不適當的熱處理 ,而在矽基板接近表面處產生的差排會在矽晶體內延伸。如果這些差排往下延伸穿過p-n介面,則形成一漏電流的通道。

透過類似圖5(a)中的試片傾轉,差排在試片厚度方向的延伸軌跡可以被分析出來。因為組成差排的矽原子和基材(Matrix)的矽原子完全相同,差排在TEM明場像中的明暗對比機構只有繞射對比,所以繞射條件影響了差排的形貌,甚至導致整條差排消失不見。要準確地分析差排,必須採用雙束繞射條件(Two Beam Diffraction Condition),加上適宜的偏移參數(Deviation Parameter)。所以從二個相距15 ~ 20度的角度分析同一組差排時,必須盡量保持同一種雙束繞射條件,以確保被分析的差排形貌在二張不同角度的TEM明場像中保持大致不變。

圖6是一組典型的TEM立體影像。圖6(a)是一在[100]正極軸拍攝的TEM明場像,二條待分析的差排分別標示處A和B,右下角鑲嵌的是對應的聚束電子繞射(CBED)圖案。圖6(b)和圖6(c)是以圖6(a)為中心處,往相反方向各傾轉約8度,但保持相同雙束繞射條件的TEM明場像。影像中, A、B二差排的間距,在圖6(b)中明顯小於在圖6(c)中(d1 < d2)。差排A和主動區邊緣(黃色虛線標註處)的距離L,在圖6(b)中則明顯大於在圖6(c)中。以上這些間距變化的現象和圖5中陳述的現象類似,此結果可以初步推論出差排A和差排B在試片的不同深度。

藉由主動區邊緣當參考線,量測差排A和差排B在二影像中轉折點和主動區邊緣的距離,再運用基本的幾何運算,推算出差排A和差排B在矽基板內的延伸軌跡如圖7所示。差排B只在試片表面延伸,但是差排A的深度達260奈米,已經貫穿p-n介面,顯然是此漏電型失效元件的漏電渠道。

TEM有助於了解材料結構/特性

TEM是目前唯一可以分析晶體材料內部晶體缺陷,例如差排等的微奈米材料分析技術。TEM除了可以分析差排的型貌、密度和種類外,藉由TEM立體影像技術還可以分析差排在矽基板內的延伸軌跡,進而判斷該差排是否貫穿p-n介面,形成一個漏電的渠道。若能深入利用TEM的功能,將可更全面地理解材料的微細結構和特性,提高元件異常的分析能力。

參考資料:

[1] J. W. Edington, Practical Electron Microscopy in Materials Science, Van Nostrand Reinhold Company, New York(1976). ISBN: 0-442-22230-0

[2] G. Thomas and M. J. Goringe, Transmission Electron Microscopy of Materials, John Wiley & Sons, Inc., New York(1979). ISBN: 0-471-122440-0

[3] David B. Williams and C. Barry Carter, in Transmission Electron Microscopy, Microscopy, part 2, Plenum Press, New York(2007). ISBN: 0-471-122440-0

[4] 鮑忠興, “穿透式電鏡三維立體成像術”,科儀新知第三十卷第二期,48-54(2008)。

[5] G.S. Liu, S.D. House, J. Kacher, M. Tanaka, K. Higashida, I.M. Robertson, “Electron tomography of dislocation structures”, Material Characterization, Vol. 87, 1-14(2014)

[6] Alexandre Mussi, Ahmed Addad, Fabien Onimus, “Dislocation electron tomography: A technique to characterize the dislocation microstructure evolution in zirconium alloys under irradiation”, Acta Materialia, Vol. 213, 116964(2021).

[7] J. S. Bow and Speed Yu, “Depth Measurement of Dislocations in Si Substrate by Stereo TEM,” Proc. ISTFA, 233-234(2005).

(本文作者為宜特科技材料分析專家)

TEM破解半導體差排軌跡 找出晶片漏電真因(2)